产品描述

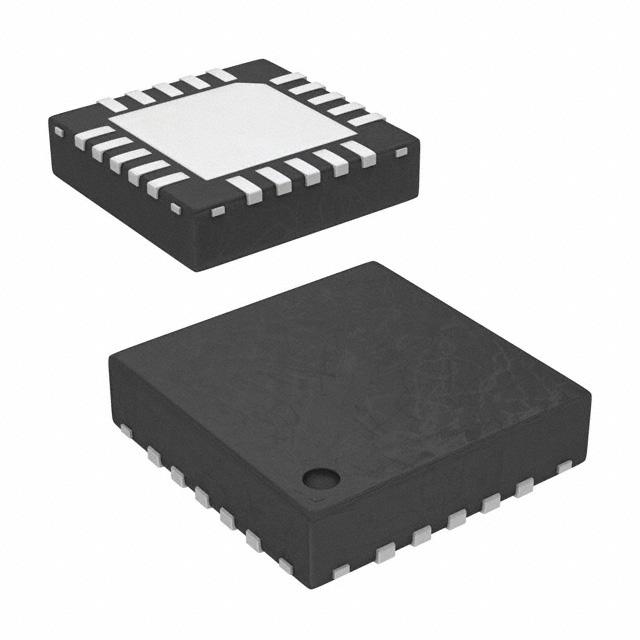

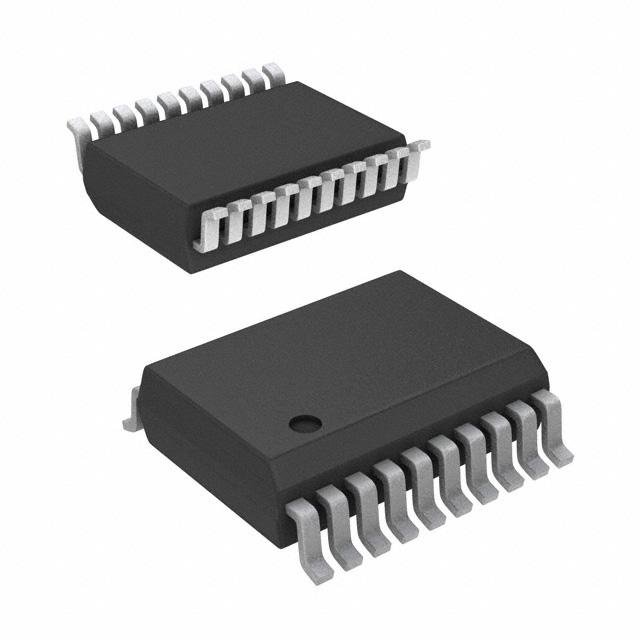

PY32F003

2. 功能概述

2.1. Arm® Cortex®-M0+ 内核

Arm® Cortex®- M0+是一款为广泛的嵌入式应用设计的入门级 32 位 Arm Cortex 处理器。它为开发人员提

供了显著的好处,包括:

结构简单,易于学习和编程

**低功耗,节能运行

精简的代码密度等

Cortex-M0+处理器是 32 位内核,面积和功耗优化高,为 2 级流水的冯诺伊曼架构。处理器通过精简但强

大的指令集和广泛优化的设计,提供高端处理硬件,包含单周期乘法器,提供了 32 位架构计算机所期望的**

性能,比其他 8 位和 16 位微控制器具有更高的代码密度。

Cortex-M0+与一个嵌套的矢量中断控制器(NVIC)紧密耦合。

2.2. 存储器

片内集成 SRAM。通过 bytes(8bits)、half-word(16bits)或者 word(32bits)的方式可访问 SRAM。

片内集成 Flash,包含两个不同的物理区域组成:

Main flash 区域,它包含应用程序和用户数据

Information 区域,4KBytes,它包括以下部分:

Option bytes

UID bytes

System memory

对 Flash main memory 的保护包括以下几种机制:

read protection(RDP),防止来自外部的访问。

wrtie protection(WRP)控制,以防止不想要的写操作(由于程序存储器指针 PC 的混乱)。写保护

的较小保护单位为 4Kbytes。

Option byte 写保护,专门的解锁设计。

2.3. Boot 模式

通过 BOOT0 pin 和 boot 配置位 nBOOT1(存放于 Option bytes 中),可选择三种不同的启动模式,如下

表所示:

表 2-1 Boot 配置

Boot mode configuration

Mode

nBOOT1 bit BOOT0 pin

X 0 选择 Main flash 作为启动区

1 1 选择 System memory 作为启动区

0 1 选择 SRAM 作为启动区

Boot loader 程序存储在 System memory,用于通过 USART 接口下载 Flash 程

您是第328108位访客

版权所有 ©2025 八方资源网 粤ICP备10089450号-8

深圳市华凡电子科技有限公司 保留所有权利.

深圳市华凡电子科技有限公司 保留所有权利.

技术支持: 八方资源网 八方供应信息 投诉举报 网站地图手机网站

地址:广东省 深圳市 宝安区 西乡街道

联系人:唐经理先生

微信帐号: